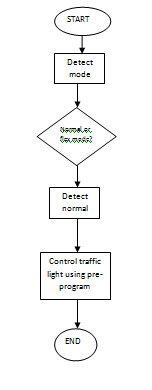

Development of flexible traffic light using verilog HDL and implemented the verilog HDL using ALTERA DE2 for proof the concept in normal mode and flex mode.

Friday, 22 March 2013

Friday, 15 March 2013

Friday, 8 March 2013

LITERATURE REVIEW

Jose E.Ortiz, Robert H.Klenke, Simple Traffic Light

Controller: A Digital Systems Design Project.Electrical And Computer

Engineering Department Virginia Commonwealth University

- This project required students to develop a state machine based controller for traffic signals at a four-way intersection. The intersection has two travel lanes in each direction; north, south, east and west. In addition, each direction has a dedicated left turn lane. Each lane contains a sensor to indicate if a car waiting at a red light. Travel lanes also contain additional sensors to indicate if cars are approaching the intersection.

Boon Kiat

Koay, Maryam Mohd Isa, Traffic Light System Design On FPGA. Proceeding of 2009

IEEE Student Conference On Research And Development, 16 – 18 November 2009, UPM

Serdang

- This project design of a low cost performance traffic light system. This type of traffic light is suitable for town and small city where sophisticated traffic light system is too costly. Written in verilog on Quartus II software and implemented on DE2 FPGA Board.

Friday, 1 March 2013

AIM N OBJECTIVES

- To develop flexible traffic light controller

- To develop verilog HDL for flexible traffic light systems

- To implement the verilog HDL using ALTERA DE2 for proof the concept

Subscribe to:

Comments (Atom)